UPC. EETAC. Bachelor degree. Second course 2A. Digital Circuits and Systems (<u>CSD</u>). Dr F. J. Robert. Grades will be available online on June 11<sup>th</sup>. Questions about the exam at <u>office time</u>. Exam 2. June 4<sup>th</sup>, 2021

## Problem 1.

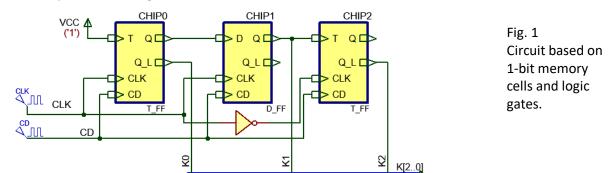

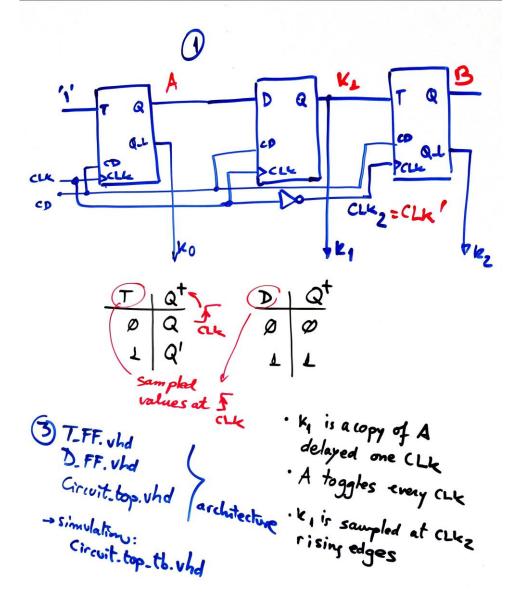

Analyse the circuit represented in Fig. 1.

(2.5p)

- 1. Determine the output vector K[2..0] drawing a <u>timing diagram</u> considering enough CLK periods.

- 2. Write down the binary codes generated.

- **3.** Explain how many VHDL files are necessary to develop and simulate the circuit using EDA tools.

## Problem 2.

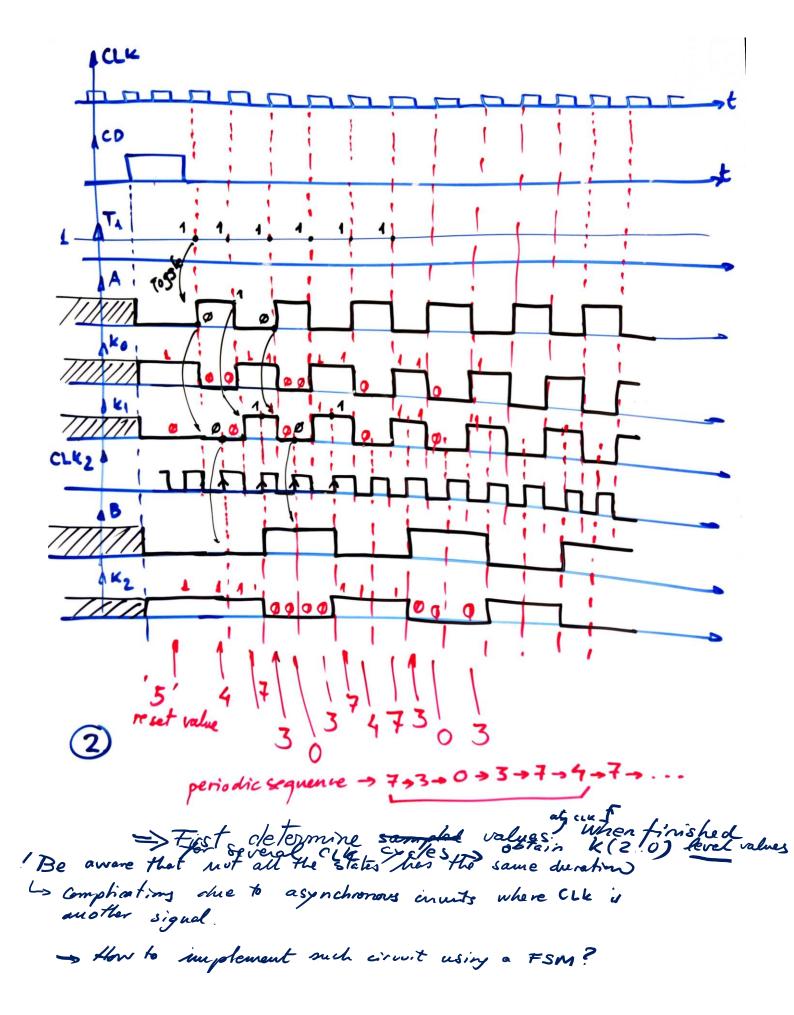

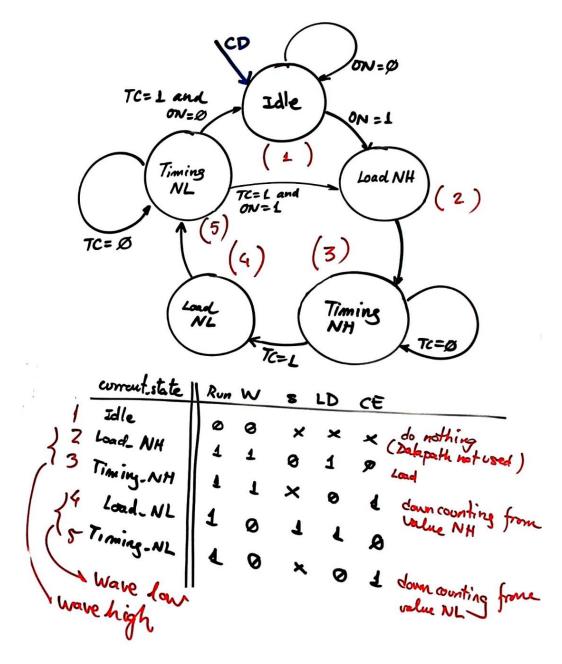

Design (specify and plan) the programmable rectangular wave generator represented in Fig. 2 using VHDL techniques and structural plan C2 for a target FPGA chip. The FSM is controlling a datapath based on a *Counter\_mod16*. The 4-bit radix-2 number **NH** establishes the number of CLK pulses where wave output (**W**) is high, **NL** establishes the number of CLK pulses where wave output (**W**) is high, **NL** establishes the number of CLK pulses where wave output (**W**) is high.

Fig. 2. a) *Wave\_gen* symbol.

b) Example W waveform when running.

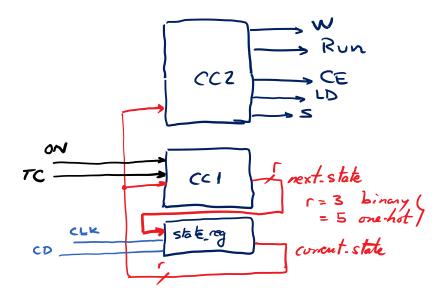

c) Proposed dedicated processor architecture for this project.

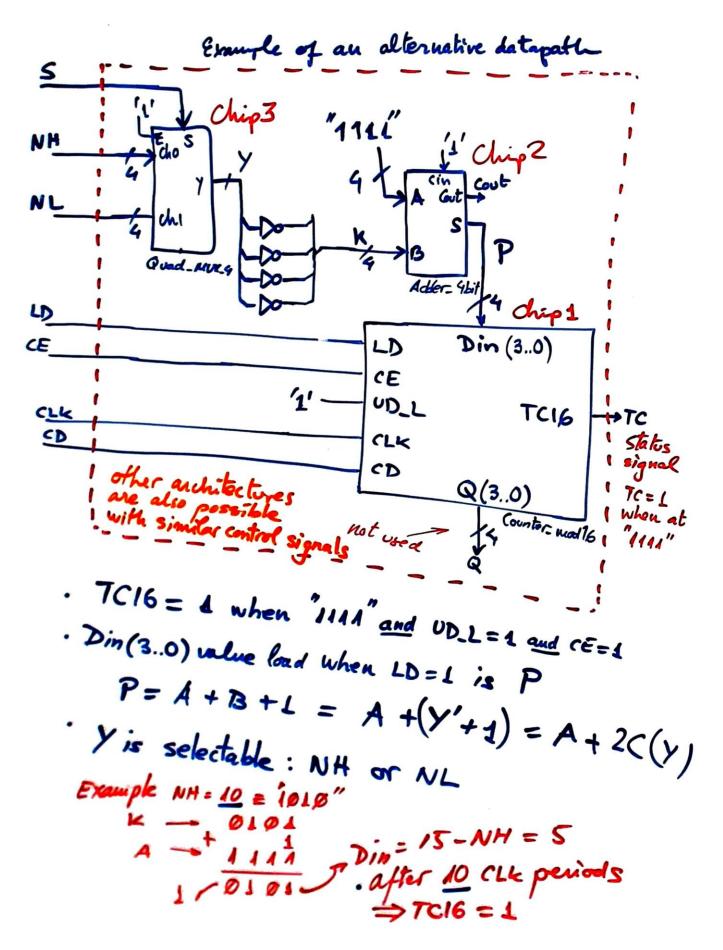

UD\_L = '0' means that the *Counter\_mod16* is configured as **down counter** and thus TC16 is a zero detector status signal to be used by the FSM.

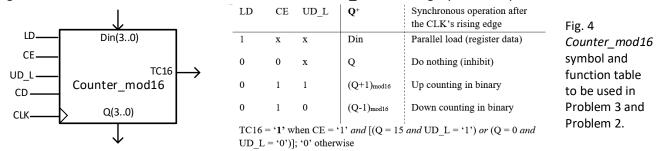

The function table of *Counter\_mod16* is in Fig. 4.

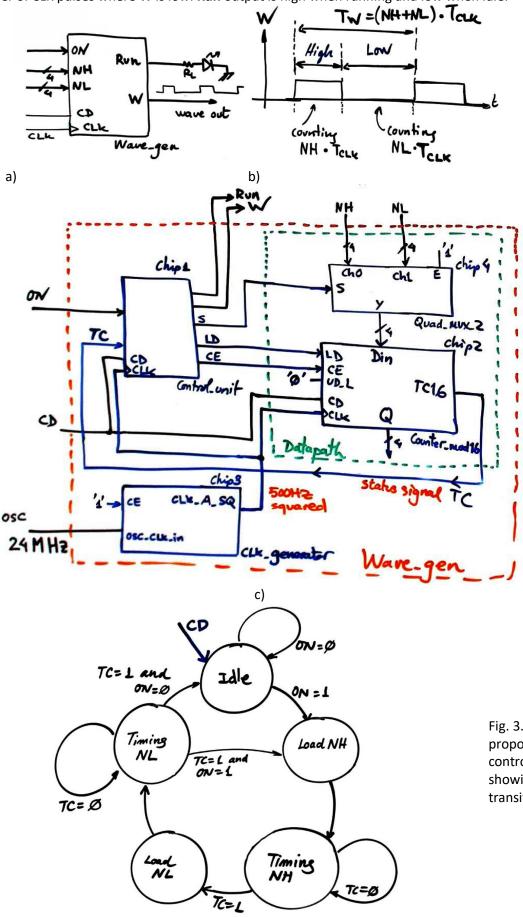

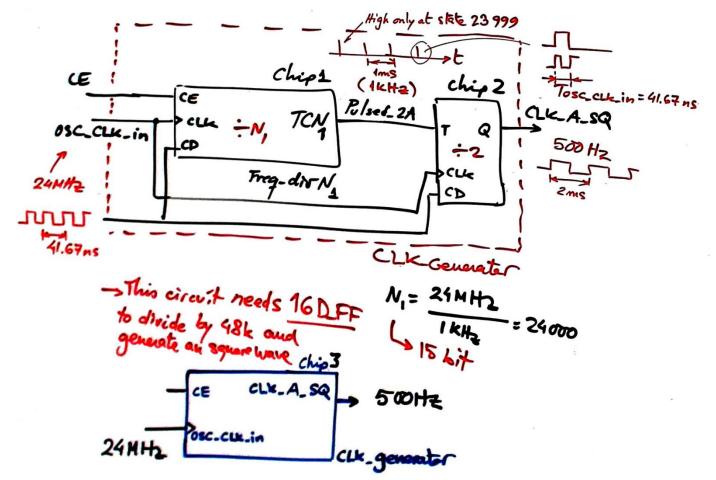

Fig. 3. State diagram proposed for Chip1 control unit (FSM) showing only states and transitions. 1. Invent the Chip3 *CLK\_Generator* to obtain a 500 Hz square wave from the 24 MHz crystal oscillator.

2. Calculate the frequency of the output rectangular wave W when NH =10 and NL = 4.

1 CLK period at Load\_NH; NH at TimingNH I CLK period at Load-NL, NL at TimingNL T = [(NH+1) + (NL+1)] Telk Tw = (11+5) 2ms > 31.25Hz - This frequency and its duty cycle [Ton/Tou] is programmable using NH and NL parameters.

3. Explain how many D\_FF register will contain this project Wave\_gen.

CLIC-Jennator -> 16 D-FF Control unit -> 5 (coding in one-hot) or 3 coding in binary or Gray Counter-wod 16 -> 4 D-FF (-> 25 or 23) D-FF

**4.** Draw the Chip1 internal FSM architecture connecting all the control unit inputs and outputs.

5. Draw the Chip1 CC2 truth table to determine all the outputs represented usually in parenthesis in Fig. 3.

6. Invent an alternative architecture for the datapath if *Counter\_mod16* is used as **up counter** with UD\_L = '1'.

## Problem 3.

Design the PIC18F4520 microcontroller version of the *Counter\_mod16* using a plan Y adaptation.

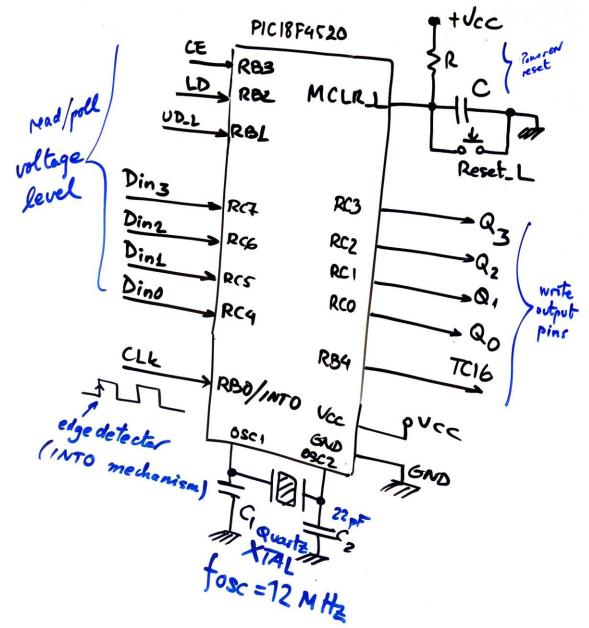

1. Draw the hardware schematic: input switches, outputs, reset (MCLR\_L) and 12 MHz quartz crystal oscillator.

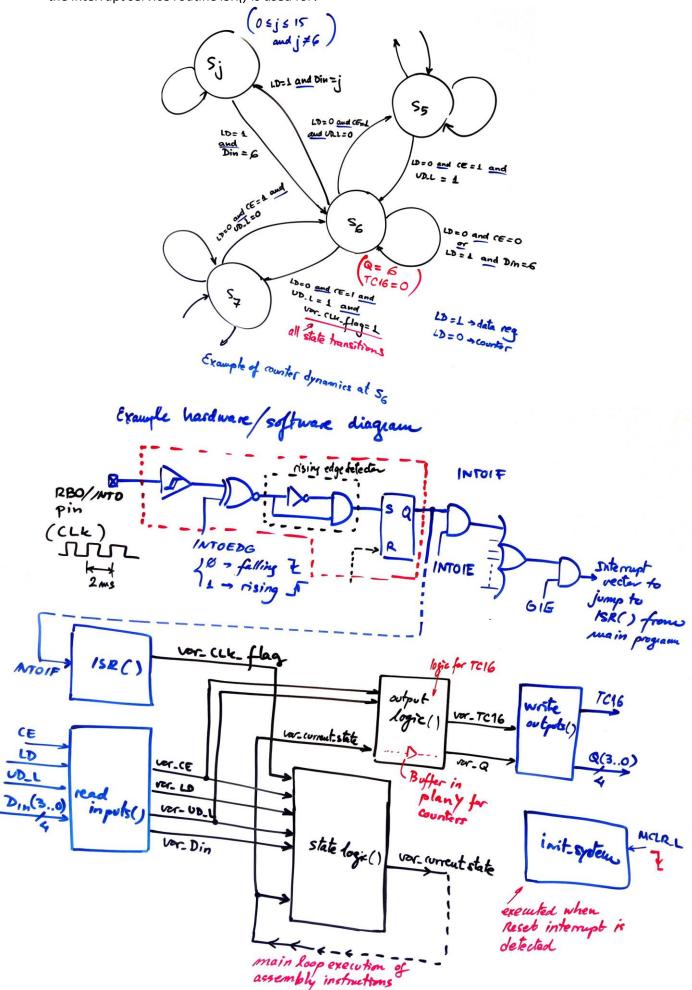

**2.** Draw the hardware-software diagram. Why the CLK for counting has to be connected to RBO/INT pin? What the interrupt service routine *ISR()* is used for?

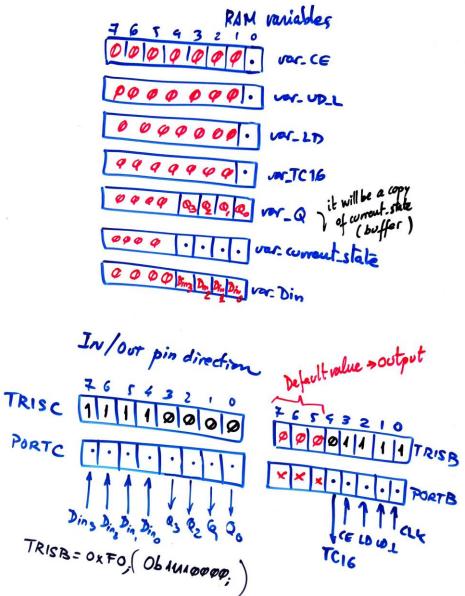

**3.** Organise and name RAM variables for the project. Explain how to configure port pins and interrupts in *init\_system()*.

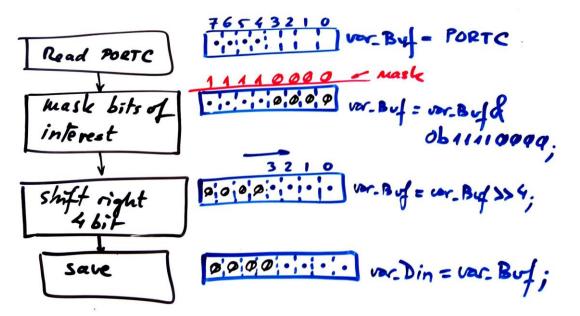

4. Explain how to poll the input values using bitwise operations in *read\_inputs()*.

Example of reading polling inputs

$$\begin{array}{c}

\mu C \\

\mu C \\

read-inputo() \\

\hline

\\

\begin{array}{c}

a \\ bin(3) \\

\hline

\\

\begin{array}{c}

a \\ c \\ c \\

\hline

\\

\begin{array}{c}

a \\ c \\ c \\

\hline

\\

\begin{array}{c}

a \\ c \\ c \\

\hline

\\

\begin{array}{c}

a \\ c \\ c \\

\hline

\\

\begin{array}{c}

a \\ c \\ c \\

\hline

\\

\begin{array}{c}

a \\ c \\ c \\

\hline

\\

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\end{array}} \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\end{array}} \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

\begin{array}{c}

a \\ c \\

\end{array}} \\

\hline

\end{array}} \\

\hline$$

} \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

} \\

\hline

\end{array}} \\

\hline

\end{array}} \\

} \\

\hline

\end{array}} \\

\end{array}} \\

\hline

\end{array}} \\

} \\

\hline

\end{array}} \\

\end{array}} \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

\end{array}} \\

\hline

} \\

\hline

} \\

\hline

} \\

T} \\

T}

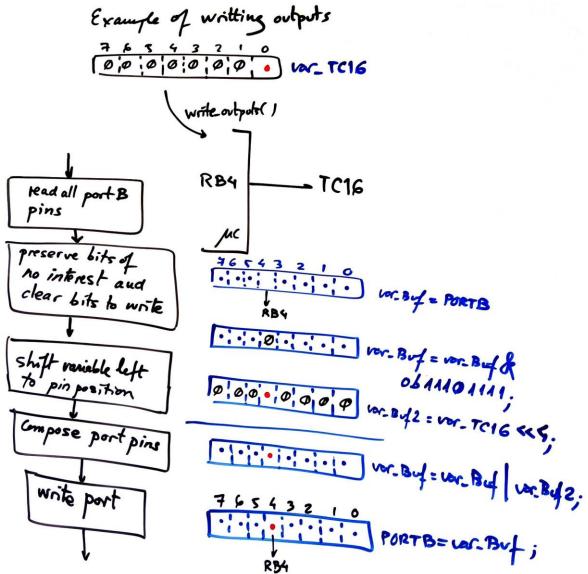

5. Explain how to drive the six outputs using bitwise operations in write\_outputs().

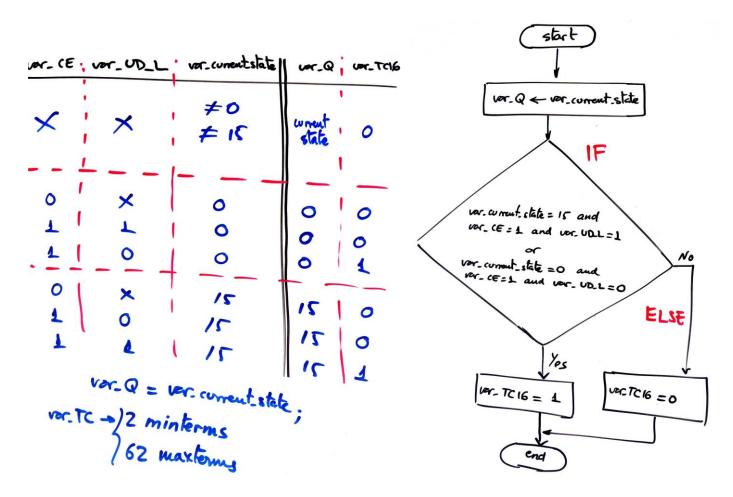

6. Draw the truth table and flowchart for the *output\_logic()*.

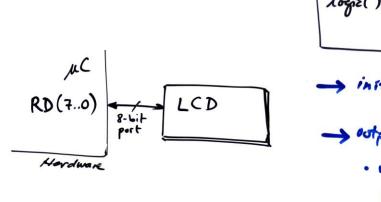

7. What functions will be modified and how if we like to add an LCD to represent counter states?

| output<br>logic()<br>shing<br>variables<br>LCD<br>library<br>LCD<br>port                  |

|-------------------------------------------------------------------------------------------|

| -> init_system () -> LCD_init() with a gin<br>hardware configuration                      |

| () SLCD_init() with a give                                                                |

| → estpot_logic() · LCD_puts("Hello world")<br>data on the off on print only               |

| · LCD_put-("                                                                              |

| · LCD_LI ("Hello world")                                                                  |

| · ver_ LCD-flag to print only new<br>data on the top print only new<br>· Sprintf( decimal |

|                                                                                           |

| Fine ( decimal in )                                                                       |

| · Sprintf ( decimal variables, etc. )                                                     |

|                                                                                           |

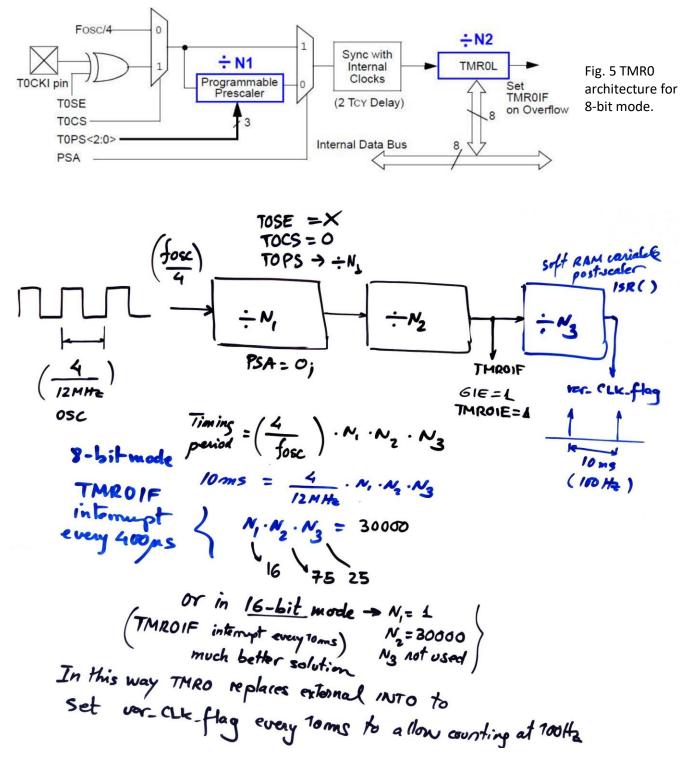

8. How to configure and program the TMR0 to replace external CLK if we require counting at 100 Hz?

(Complementary questions for developing and testing the final project using microcontroller EDA tools.)

- **9.** Draw the truth table and the flowchart for the *state\_logic()*.

- **10.** Develop the project in Proteus and MPLABX, debug and verify. This is another P10 example.

- Phase #1: Only up counting. Adapt hardware and software from the tutorial plan Y <u>Counter mod1572</u>.

- Phase #2: Up and down. This is basically modify state\_logic()

- Phase #3: Parallel data inputs. This is again basically modifying *state\_logic()*

- Phase #4: Add an LCD to represent binary and decimal unsigned numbers.