UPC. EETAC. Bachelor Degree on Telecommunications Engineering. 2A. Digital Circuits and Systems (CSD).

F. J. Robert, J. Jordana. Electronic Engineering Department

### Sample questions for projects P1-P2 - P3 - P4

For a boolean function of *n* variables  $x_1, ..., x_n$ , a sum term in which each of the *n* variables appears **once** (in either its complemented or uncomplemented form) is called a **maxterm**.

A single maxterm *n* gives a '0' value for just one combination of the input variables. Thus, it is possible to write the truth table of a logical function as a product of maxterms.

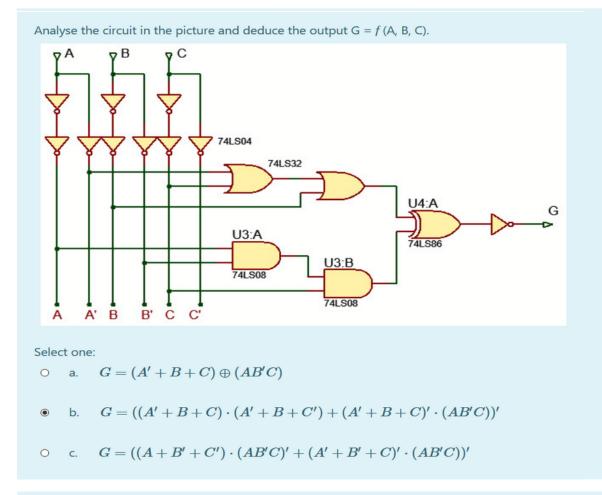

#### Select one:

### Answers

- True

- O False

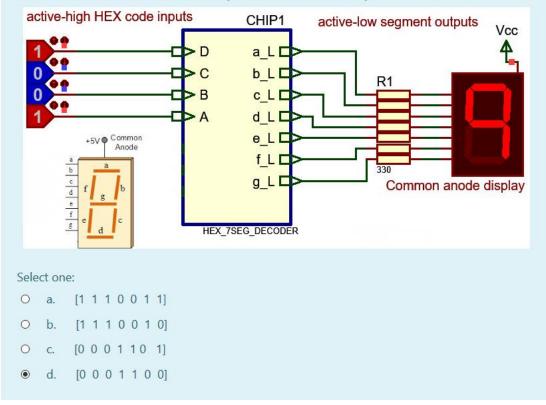

This circuit is a hexadecimal to seven-segment decoder which has active-low outputs. The number '9' is represented. Which is the value of the output vector  $[a\_L, b\_L, c\_L, \dots, g\_L]$ ?

The picture shows the truth table resulting from the WolphamAlpha numerical engine when ordered to obtain it. The function is described as: P = f(D1, D0, A, B) Thus, find the sum of minterms.

| th tal | ble: |    |    |   |     |       |       |

|--------|------|----|----|---|-----|-------|-------|

| Α      | В    | D0 | D1 | Р |     |       |       |

| Т      | Т    | Т  | Т  | Т |     |       |       |

| Т      | Т    | Т  | F  | Т |     |       |       |

| Т      | Т    | F  | Т  | F |     |       |       |

| Т      | Т    | F  | F  | F | Sel | ect o | ne:   |

| Т      | F    | Т  | Т  | F | ۲   | a.    | P = f |

| Т      | F    | Т  | F  | Т |     |       |       |

| Т      | F    | F  | Т  | Т | 0   | b.    | P = f |

| Т      | F    | F  | F  | Т |     |       |       |

| F      | Т    | Т  | Т  | F | 0   | C.    | P = f |

| F      | Т    | Т  | F  | F |     |       |       |

| F      | Т    | F  | Т  | Т |     |       |       |

| F      | Т    | F  | F  | Т |     |       |       |

| F      | F    | Т  | Т  | Т |     |       |       |

| F      | F    | Т  | F  | F |     |       |       |

| F      | F    | F  | Т  | F |     |       |       |

| F      | F    | F  | F  | Т |     |       |       |

- a.  $P = f(D1, D0, A, B) = \sum m(0, 1, 2, 6, 7, 9, 10, 12, 15)$

- o b.  $P = f(D1, D0, A, B) = \sum M(3, 4, 5, 8, 11, 13, 14)$

c.

$$P = f(D1, D0, A, B) = \sum m(0, 1, 5, 6, 7, 10, 11, 12, 15)$$

This circuit is build using gates of the HCT (High Speed CMOS) technology that has the characteristics given below. Which statement is false?

| 1<br>2<br>74HCT00           | Vo1             | Vi:  |         | HCT86   |       |

|-----------------------------|-----------------|------|---------|---------|-------|

| DC Electrical Sp            | ecification     | E.   | 0000000 | = 4.5 V |       |

| PARAMETER                   | SYMBOL          | MIN  | 25°C    | MAX     | UNITS |

| HC TYPES                    |                 |      |         |         |       |

| High Level Input<br>Voltage | VIH             | 3.15 | -       | -       | V     |

| Low Level Input             | V <sub>IL</sub> |      | _       |         |       |

| Voltage                     |                 | -    | -       | 1.35    | V     |

| High Level Output           | VOH             | _    |         |         |       |

| Voltage                     |                 | 4.4  | -       | -       | V     |

| Low Level Output<br>Voltage | Vol             |      | 2       |         |       |

|                             |                 |      |         | 0.1     | V     |

Select one:

- $\circ~$  a.  $~V_{IL\ max}$  is the maximum voltage that can understand  $V_{i2}$  as a logic '0'

- $\odot$  b. In good operation conditions, when generating a low '0',  $V_{O1}$  can be higher that  $V_{OL\,max}$  = 0.1 V

- $\circ~$  c. If  $V_{O1}$  is below the the  $V_{OH\,min}~$  = 4.4 V the next gate input voltage  $V_{i2}$  may not understand it as a valid '1' .

- $\circ~$  d. If the NAND gate is operating correctly, when generating an output level '1', V\_{O1} is always above the threshold V\_{OH min}~= 4.4 V

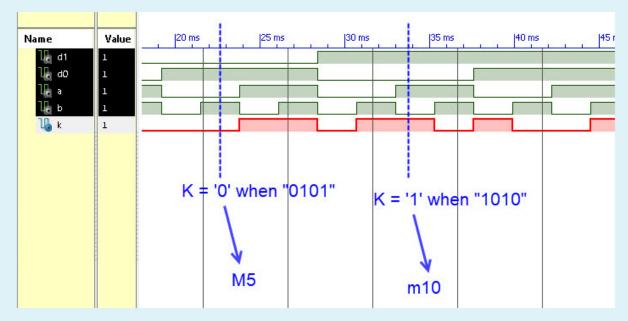

Running the EDA VHDL simulator and examining the output timing diagram we can determine the truth table of a given circuit. For instance, in the capture below, we measure that:

$K = f(D1, D0, A, B) = K(1100) = 0 \rightarrow M_{12}$

$$K(1001) = 1 \rightarrow m_9$$

# Select one:

# Answers

- o True

- False

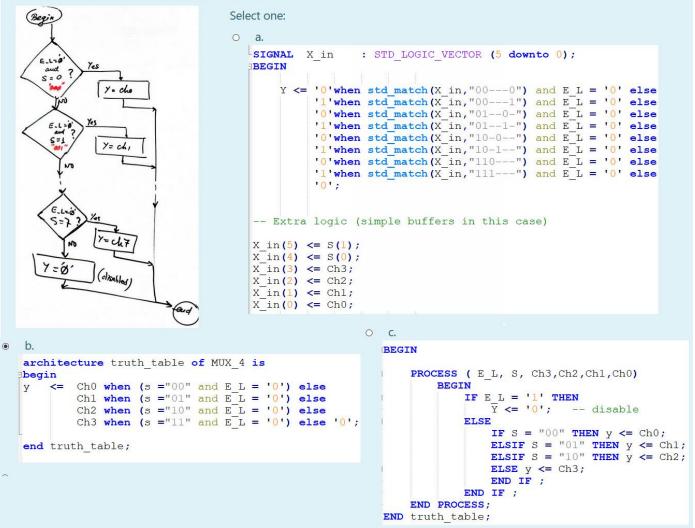

We plan a VHDL behavioural description of a **MUX\_8** as shown in the flow chart sketch below. We have found up to three possible circuits to **copy & adapt** from the *digsys* web belonging to MUX\_4 projects. Which is preferred one?

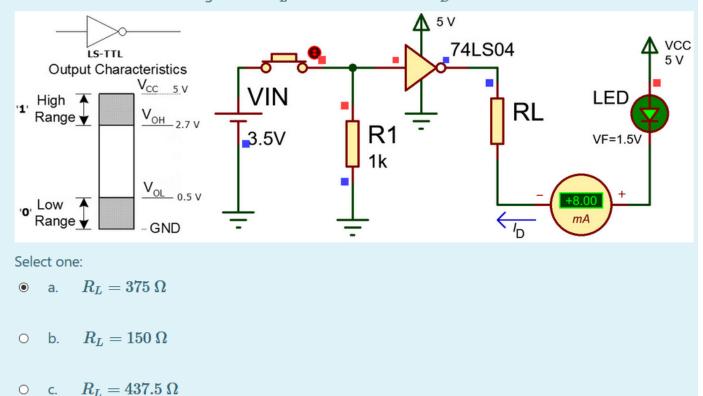

Which is the value of the limiting resistor  $R_L$  that bias the LED with  $I_D = 8mA$  in the worst case scenario?

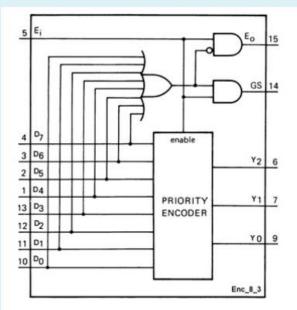

This is a HEF4532B, a commercial encoder 8 to 3 with priority high. How many minterms have the outputs GS and Y0?

| 16              | 15             | 14             | 13 | 12<br>D <sub>2</sub> | 11             | 10             | 9               |

|-----------------|----------------|----------------|----|----------------------|----------------|----------------|-----------------|

| V <sub>DD</sub> | Eo             | GS             | D3 | D2                   | D <sub>1</sub> | D <sub>0</sub> | YO              |

| Þ               |                |                |    | 5328                 |                |                |                 |

| D4              | D <sub>5</sub> | D <sub>6</sub> | D7 | E <sub>i</sub>       | Y2             | Y1             | v <sub>ss</sub> |

| 1               | 2              | 3              | 4  | 5                    | 6              | 7              | 8               |

|    | inputs |    |    |    |    |    |    | outputs |    |    |    |    |    |

|----|--------|----|----|----|----|----|----|---------|----|----|----|----|----|

| Ei | D7     | D6 | D5 | D4 | D3 | D2 | D1 | D0      | GS | Y2 | Y1 | YO | Eo |

| 0  | x      | х  | х  | х  | x  | х  | х  | х       | 0  | 0  | 0  | 0  | 0  |

| 1  | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0       | 0  | 0  | 0  | 0  | 1  |

| 1  | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 1       | 1  | 0  | 0  | 0  | 0  |

| 1  | 0      | 0  | 0  | 0  | 0  | 0  | 1  | x       | 1  | 0  | 0  | 1  | 0  |

| 1  | i o    | 0  | 0  | 0  | 0  | 1  | x  | х       | 1  | 0  | 1  | 0  | 0  |

| 1  | 0      | 0  | 0  | 0  | 1  | х  | x  | х       | 1  | 0  | 1  | 1  | 0  |

| 1  | 0      | 0  | 0  | 1  | x  | x  | x  | x       | 1  | 1  | 0  | 0  | 0  |

| 1  | 0      | 0  | 1  | x  | x  | x  | x  | x       | 1  | 1  | 0  | 1  | 0  |

| 1  | 0      | 1  | x  | x  | x  | x  | x  | x       | 1  | 1  | 1  | 0  | 0  |

| 1  | 1      | x  | x  | x  | x  | x  | x  | x       | 1  | 1  | 1  | 1  | 0  |

## Select one:

о **а**.

GS has 8 minterms and YO has 6 minterms.

• b.

GS has 255 minterms and YO has 170 minterms.

О С.

GS has 2 minterms and YO has 6 minterms.

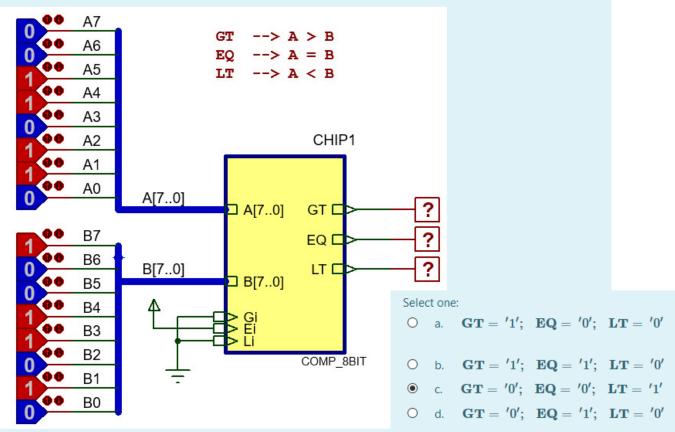

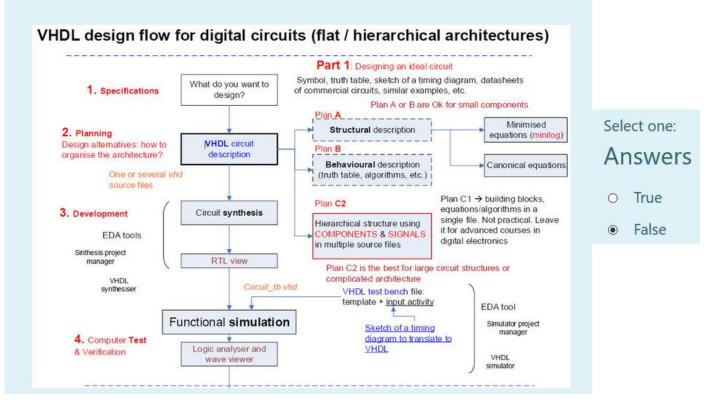

The circuit in the picture is a *Comp\_8bit*, a comparator of radix-2 binary numbers. Which is the output of the circuit when driven by these input vectors?

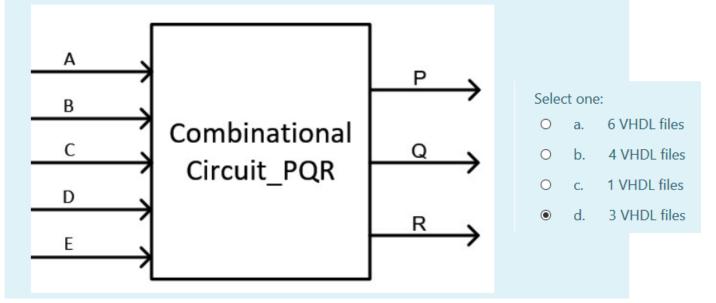

The *Circuit\_PQR* in the picture is planned on the method of decoders, and the decoder is build internally chaining 4 components *DEC\_3\_8*. How many VHDL files will contain this hierarchical structural project?

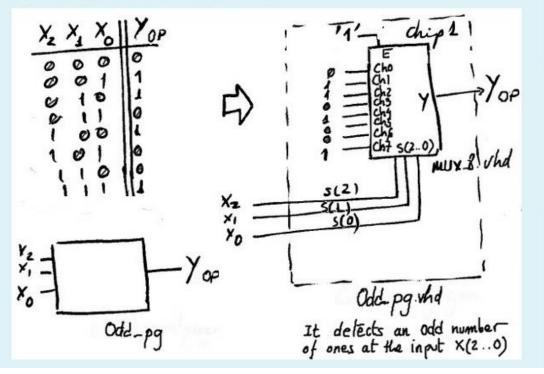

The circuit below is a 3-bit odd-parity generator solved using the method of multiplexers and a MUX\_8. Furthermore, the MUX\_8 component is build internally using MUX\_2. The resulting  $Y_{OP} = f(X_2, X_1, X_0)$  is faster (less propagation delay) than the circuit produced using maxterms  $Y_{OP} = f(X_2, X_1, X_0) = \prod\{0, 3, 5, 6\}$

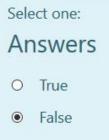

The step number 4 in this design flow, the functional simulation, allows you to measure gate delays, propagation times and the worst case scenario to deduce the maximum frequency of operation of the designed circuit.

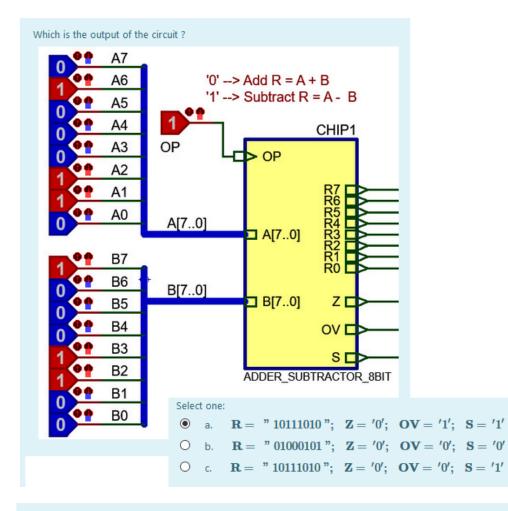

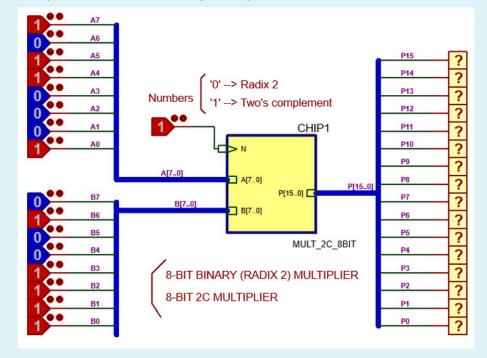

The circuit in the picture is a *Mult\_2C\_8bits*, a binary multiplier that has a control input **N** to operate with radix 2 data when  $\mathbf{N} = 0$ , and with two's complement data when  $\mathbf{N} = 1$ . Which is the output of the circuit when driven by these input vectors?

Select one:

• a. P(15..0) = "1110 0111 1001 1111 "

O b. P(15..0) = "1001 1111 0111 1111 "

O c. P(15..0) = 0011 0110 1001 1111 "

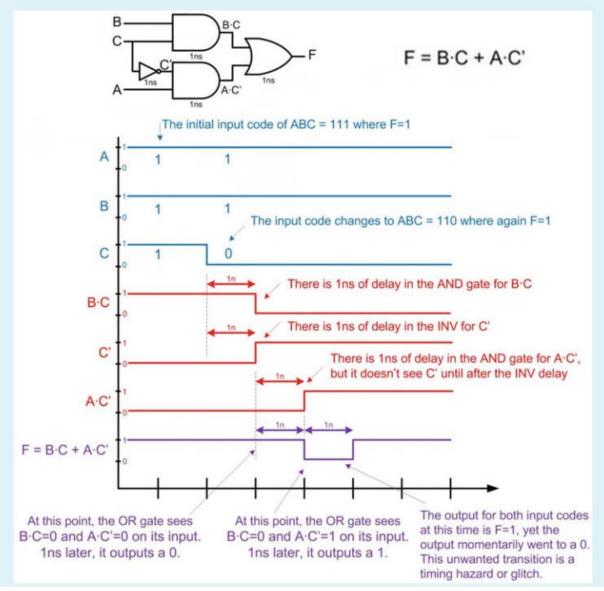

Timing hazards or glitches refer to unwanted transitions on the output of a combinational logic circuit. These are most commonly due to different delay paths through the gates in the circuit. In real circuitry there is always a finite propagation delay through each gate. Consider the circuit analysed below where a timing diagram shows signal transitions and hand-made annotations.

### Select one:

- O a. Using VHDL test benches we can measure the circuit's delay such as here (3 ns) using the functional simulation EDA tool.

- Using VHDL test benches we can measure the circuit's delay such as here (3 ns) using the gate-level simulation EDA tool.

- O c. Using VHDL test benches we can measure the circuit's delay such as here (2 ns) using the gate-level simulation EDA tool.

- Using VHDL test benches we can measure the circuit's delay such as here (2 ns) using the functional simulation EDA tool.

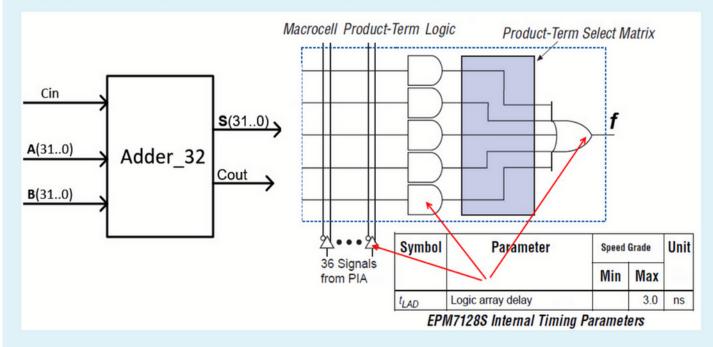

The *Adder\_32* entity in the picture is based on the ripple-carry technique of 32 *Adder\_1bit* cells, which internally are structured using 3-levels-of-logic gates as shown in the simplified macrocell. The entity is implemented in an Intel-Altera CPLD MAX7128S chip showing the characteristics in the table. Calculate the propagation delay and the maximum speed of operation.

Select one:

| Оа. | $t_P =$ | 96 ns; | $f_{max} =$ | $10.4 \ MHz$ |

|-----|---------|--------|-------------|--------------|

|-----|---------|--------|-------------|--------------|

- $oldsymbol{O}$  b.  $t_P = 288 \ ns; f_{max} = 1.73 \ MHz$

- $\bigcirc$  c.  $t_P=3~ns; f_{max}=333.3~MHz$