# Sample P5-P6 questions

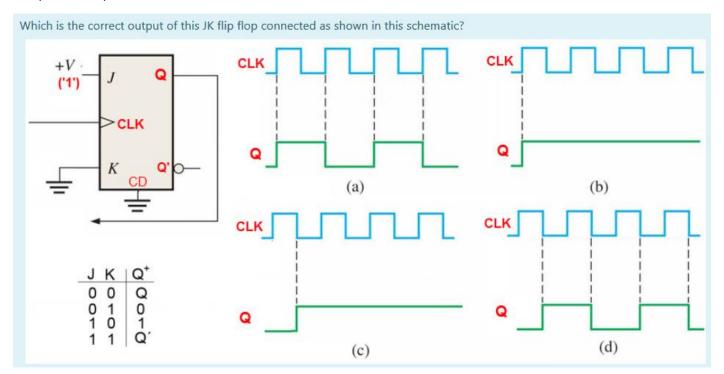

#### Select one:

- O 1. Waveforms d)

- 2. Waveforms b)

- O 3. Waveforms c)

- O 4. Waveforms a)

Here we are a pair of symbols and an example of timing diagram for a 1-bit memory cell. The correct symbol that corresponds to the waveforms is the b). set input-Reset input Ø RS\_Latoh RS\_Latch a) 5.050000 us the '1' is saved the '0' is saved Select one: 15 us 5 us 10 us 25 us Name Value 0 us Answers True False set reset unknown Simulation of the order order unpredictable situation

# Examining the VHDL code below we can deduce that:

```

ARCHITECTURE structure OF circuit IS

COMPONENT T FF IS

Port (

CLK

: IN STD LOGIC;

: IN

CD

STD LOGIC;

STD LOGIC;

: IN

: OUT STD LOGIC

);

END COMPONENT;

SIGNAL K : STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

Chip1 : T_FF

PORT MAP (

CLK

=> CLK,

CD

=> CD,

=> '1',

T

=> K(0)

Q

);

Chip2

: T FF

PORT MAP (

CLK

=> K(0),

CD

=> CD,

=> '1',

T

Q

=> K(1)

);

Chip3 : T FF

PORT MAP (

CLK

=> K(1),

=> CD,

CD

=> '1',

T

=> K(2)

);

Chip4

: T FF

PORT MAP (

CLK

=> K(2),

CD

=> CD,

=> '1',

\mathbf{T}

=> K(3)

Q

);

Q <= K;

END structure;

```

- O a. It corresponds to a synchronous circuit based on T\_FF.

- b. It corresponds to an asynchronous circuit based on T FF.

- O c. Because we have no information on the entity description, we can not deduce whether the system has a common CLK for synchronicity.

- O d. T\_FF cannot be connected in this way, because their outputs cannot be determined.

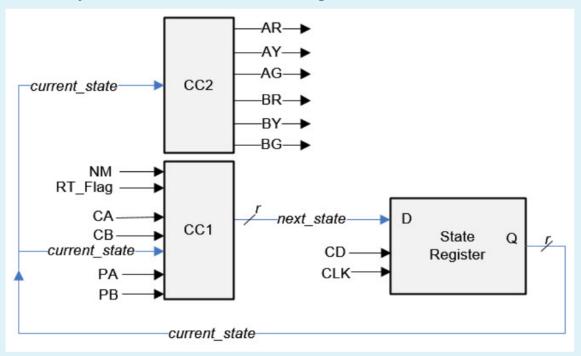

The schematic below represents the internal architecture of a FSM to control a traffic light system. 6 outputs drive the coloured lamps and 6 inputs from several sensors and buttons determine how the machine works. The FSM has 5 states and they are coded in *one-hot*. Which one is the right answer?

- o a. It is not possible to encode the machine using *one-hot* code (00001, 00010, 00100, 01000, 10000) because binary sequential is required (000, 001, 010, 011, 100, 101).

- O b. The state register contains 3 DFF; CC1 is a truth table that contains 512 combinations; CC2 has a truth table that contains 8 combinations

- c. The state register contains 5 DFF; CC1 is a truth table that contains 2048 combinations; CC2 has a truth table that contains 32 combinations.

- O d. The state register contains 5 DFF; CC1 is a truth table that contains 512 combinations; CC2 has a truth table that contains 64 combinations.

# Example questions for the P7-P8 questionnaire

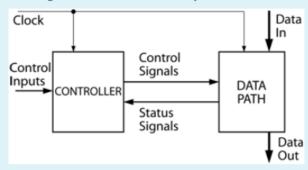

In datapath there are registers to save operants and results, an arithmetic and logic unit (ALU) and other combinational circuits.

The function of the status signals from the datapath to the controller FSM is to inform about the result of the operations (flags), for instance zero, carry out, negative, overflow, division by zero, etc.

Select one:

### Answers

- True

- False

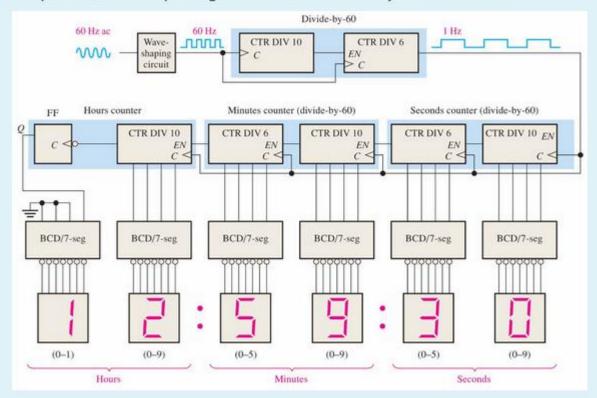

This is a schematic copied from the book T. L. Floyd, Digital Fundamentals, 9th ed., Prentice Hall, 2006. It is a design of a real-time clock that has HH:MM:SS BCD outputs. The names of the components and signals has not been adapted to our CSD naming style, but they are very similar. The wave-shaping circuit is analogue.

The question, after inspecting the circuit, is: how many D-FF it contains?

- O a. The circuit contains 59 data registers D-FF

- b. The circuit contains 14 data registers D-FF

- c. The circuit contains 26 data registers D-FF

- d. The circuit contains 192 data registers D-FF

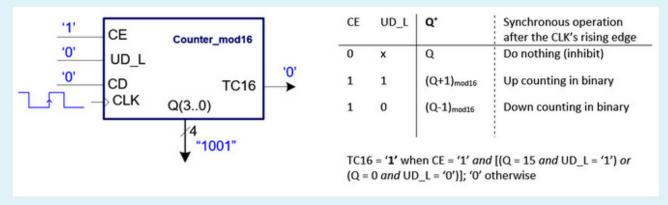

With respect to the Counter\_mod16 in the picture below, which is the next state after the CLK's rising edge?

# Select one:

- a. "1000"

- O b. "1011"

- O c. "1001", because the system is disabled or inhibited

- O d. "1100"

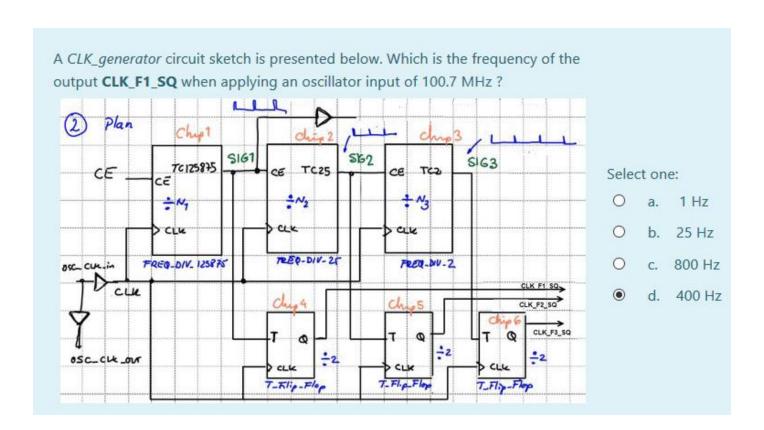

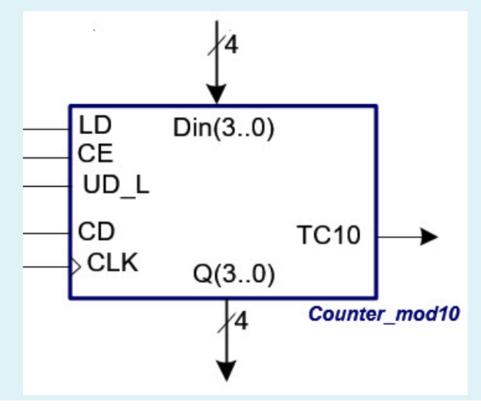

Using and interconnecting 3 universal counters modulo 10 (*Counter\_mod10*) like the one depicted below and other components like logic gates, we can design many different counters. Which is the maximum modulo that can be attained when connected in cascade?

- O a. Counter\_mod100

- b. Counter\_mod1000

- O c. Counter\_mod30

- O d. Counter\_mod300