|

|

|||||

Chapter 2 problems |

- D2.7 - |

Dumbwaiter or simple lift (FPGA-VHDL) |

|||

|

|

|||||

1. Specifications

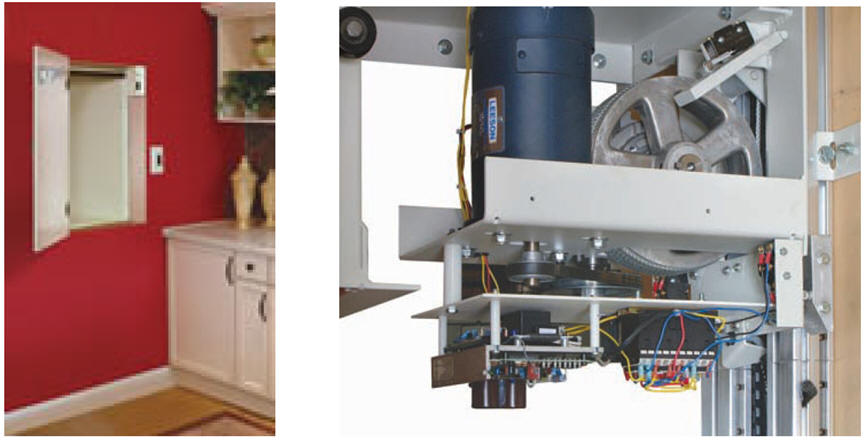

Our company has to design the control system for a simple dumbwaiter (a small freight elevator used to transport food, wine, and other items between storeys of a residential building) ordered by our client. It will transport loads between a 2-storeys kitchen. Fig. 1 shows a photograph of an installed commercial dumbwaiter and a detail of the motor and the control system installed under the car.

The same project designed programming a μC is in D3.7.

|

|

Fig. 1. Photograph of a commercial dumbwaiter. |

Some questions and ideas to kick off the project and organise it in five sections. Apply the FSM architecture to this problem.

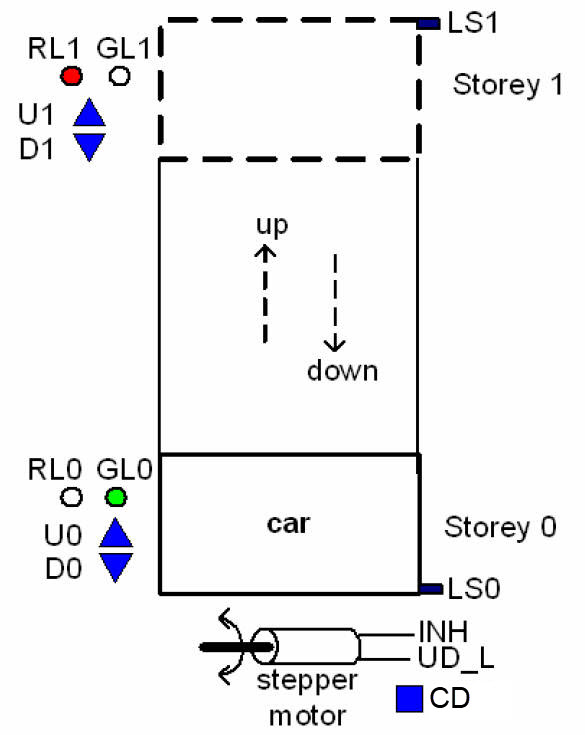

Produce a sketch of the dumbwaiter system that includes up and down buttons for both levels, location of the floor sensors, green and red LED's, and outputs for driving the stepper motor. See Fig. 2.

- U1, D1, U0, D0: buttons for calling the car.

- LS1, LS0: limit switches to detect the presence/absence of the car stopped at each storey.

- CD: if pressed or after power on, this special signal takes the car to the initial state stopping the car at storey 0.

- GL1, RL1, GL0, RL0: LEDs for indicating operation: green LED is ON when the car is stopped in the corresponding storey, red LED is ON when the car is moving between storeys.

- INH: when high this signal inhibits the motor movement.

- UD_L: when INH is not asserted, this signal generates up movement when high and down movement when low.

|

|

Fig. 2. Sketch of the 2 storeys dumbwaiter indicating sensors, pushbuttons and output functions to drive the stepper motor and the LED. |

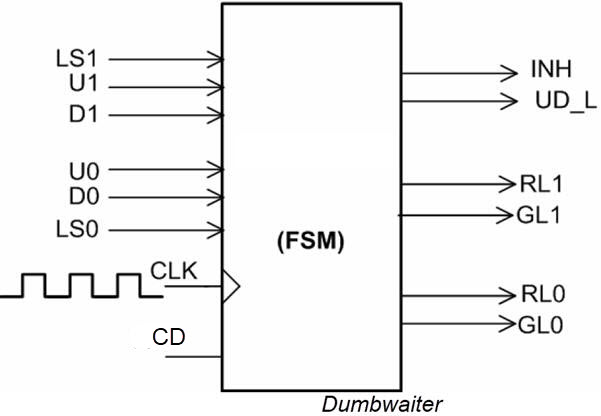

Draw the symbol of the entity to be designed.

|

|

Fig. 3. Symbol. |

It is a good idea at this point, to discuss what logic levels to consider from the pushbuttons and switches. For instance, LS1 and LS0 will never be '1' at the same time. They will be '0' when the car is in transit between storeys. If the car is at storey 1, clicking U1 will have no effect, and when the car is stopped at storey 0, clicking D0 has no effect. When the car is in transit, clicking buttons has no efffect.

NOTE: The idea is to read and study as much as you like materials, books, examples or advanced tutorials, but do not copy from them. Your aim is to imagine that this project is derived from the LAB6 tutorial where we organised a FSM controlled clicking a single button. The better you comprehend the laboratory tutorial the faster will you design this application.

Sketch a timing diagram showing the main operations.

Infer and draw the state diagram. Annotate state transitions and outputs.

|

|

Fig. 4. State diagram. |

Adapt the FSM architecture to this problem, naming and connecting all signals and inputs and outputs. Draw the state register if coding the machine using the following options.

Deduce how many D_FF are required when encoding FSM states using the following options and draw the state register memory:

Option #1: radix-2 (sequential)

Option #2: Gray

Option #3: Johnson

Option #4: one-hot

Draw the state register memory block.

Write the CC2 truth table to obtain the outputs of the circuit and its flowchart.

Write the CC1 truth table to obtain the next state to go and its flowchart.

Project location:

C:\CSD\P6\dumbwaiter\(files)

Write the truth table of CC2 and CC1 and their equivalent behavioural interpretations (plan B) using flowcharts.

Write the FSM VHDL file.

Start a Quartus Prime synthesis project for one of the following programmable target chips:

Option #1: Cyclone IV EP4CE115F29C7

Option #2: MAX II EPM2210F324C3

Inspect and annotate the RTL and technology views. Check the number of D_FF synthesised in this application.

Generate a VHDL testbench fixture schematic. Translate the timing diagram sketch from the specifications into de corresponding stimulus processes.

Run functional simulations to verify your design. Visualise as well in the wave timing diagram the internal states.

Run gate-level simulations to measure the propagation time CLK to output (tCO). Measure the minimum TCLK period or the maximum frequency of operation of the FSM.

Optional: A security enhancement for preventing user accidents can be added in a new design phase #2. Install sensors switches (DS1, DS0) and electric drop bolt locks (DL1, DL0) in the storey doors, so that the car does not move unless doors are closed, and they do not open while the car is in transit or is not yet stopped in the corrresponding storey.

|

|

Fig. 5. Example of an storey door secured with an electric drop bolt lock (ref.). The idea is to keep the storey doors closed while the car is in transit |

Optional: Design the CLK generator circuit from a 50 MHz quartz crystal oscillator to obtain the CLK signal required to drive the stepper motor. Let us imagine that the driver is the D2.2. Let us rotate the motor at three revolutions per second. Deduce the number of D_FF that it will contain. Build a prototype for the DE10-Lite board assigning pins and uploading the configuration file to the FPGA.